# CONFERENCE PROGRAM

LOOKING TOWARDS THE FUTURE

BCICTS 2024

IEEE BiCMOS and Compound

Semiconductor Integrated Circuits

and Technology Symposium

October 27-30, 2024 Ft Lauderdale, FL USA

Sponsored by

The Electron Devices Society of The Institute of Electrical and Electronic Engineers

In Cooperation with

The IEEE Solid - State Circuits

Society The IEEE Microwave Theory &

Techniques Society

CONFERENCE WEBSITE www.bcicts.org

# **WELCOME FROM THE BCICTS 2024 CHAIRS**

With great pleasure we welcome you to participate in the 2024 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS). After 42 years of the Compound Semiconductor IC Symposium (CSICS), and 35 years of the Bipolar/BiCMOS Circuit and Technology Meeting (BCTM), the seventh meeting of this combined symposium will be held in person from Sunday October 27th to Wednesday October 30th at the W Fort Lauderdale, Florida, USA.

The planning committee looks forward with great anticipation at this opportunity to meet in person again, just like the last two years, after holding two BCICTS conferences virtually due to the COVID-19 pandemic. This a great opportunity for us in the engineering and technical community to reconnect with each other both professionally and personally, to meet new colleagues and visit with long-time friends, while catching up on the latest trends within microelectronics.

This year, BCICTS will continue the long history, from BCTM and CSICS, of international symposiums where distinguished experts present their latest results in bipolar, Si/SiGe BiCMOS, and compound semiconductor circuits, devices, and technology. There are no other events in the world where you can see leading edge bipolar/BiCMOS devices and technology, 5G/6G ICs, GaN HPAs, InP THz PAs, optical CMOS/SiGe transceivers, GaN HEMT power devices, advances in modeling and simulations and device physics, all presented together.

This seventh BCICTS includes presentations from worldwide submissions on all aspects of the technologies. Topics span process technology, device advances, TCAD modeling, compact modeling to IC design and testing, high-volume manufacturing, and system applications. BCICTS will also feature the very latest results in RF/microwave, millimeterwave, THz, analog & mixed signal, and optoelectronic integrated circuits.

This year, as we have done in past years, BCICTS will offer a topical short course and a more basic primer course. Both will be taught by leading experts, with the short course intended for professionals seeking comprehensive understanding of the latest industry trends and techniques, and the primer as an introductory tutorial.

We would like to thank the many dedicated volunteers on the BCICTS Committee, and the generous support of the IEEE Electron Devices, Microwave Theory and Techniques, and Solid-State Circuits Societies. Finally, we look forward to interacting with all participants to continue the traditions of technical excellence for BCICTS!

Tomislav Suligoj, Symposium Chair University of Zagreb Breandán Ó hAnnaidh, Symposium Co-Chair Analog Devices

# KEY EVENT INFORMATION

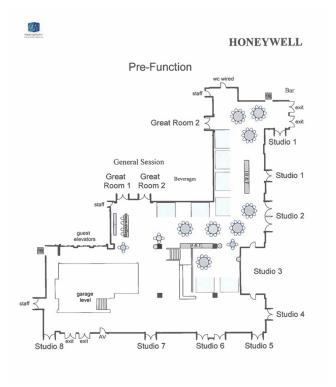

# **Meeting Locations:**

\*Registration is required for attendance

- Sunday: Short course, Studio 2&3

- Sunday: Primer, Studio#4

- Monday Wednesday:

- General Session: Ballroom

- Breakout: Studio 2,3,4

- Exhibition: Main Foyer

- Attendee Lounge & Speaker Ready Room: Studio 1

# **Conference Networking & Social Events:**

Several networking events have been arranged to promote informal social interactions among conference participants. Event details are listed below for your reference:

# Monday, October 28: Exhibitor Reception

from 5:30 PM - 7:30 PM Location: Ballroom

# Tuesday, October 29:

- Exhibitor Breakfast: 7:30 AM 8:30 AM

- Exhibitor Luncheon: 12:30 PM 2:00 PM

Location: Ballroom Foyer

# **Registration Desk Hours:**

Sunday - Tuesday: 7:30 AM - 5:00 PM Wednesday: 7:30 AM - 4:00 PM

# We're looking forward to seeing you in Fort Lauderdale, Florida!

If you have any questions, please feel free to contact Catherine Shaw:

Catherine Shaw, CMP Executive Director, Meetings and Events (BCICTS) Phone: 732-501-3334

E-mail: cs@cshawevents.com

# 2024 BCICTS SCHEDULE AT A GLANCE

|                       | SUNDAY – OCTOBER 27                                                                              |  |  |  |  |  |

|-----------------------|--------------------------------------------------------------------------------------------------|--|--|--|--|--|

| How to                | SHORT COURSE  How to Grow and Model High Reliability III-V Semiconductor Devices Studio 2&3      |  |  |  |  |  |

| 7:30AM<br>5:00PM      | Registration for Short Course Only Foyer                                                         |  |  |  |  |  |

| 8:00AM<br>8:45AM      | Breakfast for Short Course Only Foyer                                                            |  |  |  |  |  |

| 8:45AM<br>8:50AM      | Welcome & Speaker Introduction, Doug Weiser, Texas Instruments Studio 2&3                        |  |  |  |  |  |

| 8:50AM<br>10:20A<br>M | Epi Growth Dr. Edwin L. Piner Texas State University Studio 2&3                                  |  |  |  |  |  |

| 10:20A<br>M<br>10:35A | Coffee Break for Short Course Only<br>Ballroom Foyer                                             |  |  |  |  |  |

| 10:35A<br>M<br>12:05P | Process/Reliability - Dr. Jose Jimenez Qorvo<br>Studio 2&3                                       |  |  |  |  |  |

| 12:05P<br>M<br>1:15PM | Lunch Break for Short Course Only Studio 5                                                       |  |  |  |  |  |

| 1:15PM<br>2:45PM      | Device and Compact Modeling of InP HBTs Dr. Markus Müller TU Dresden, Rohde & Schwarz Studio 2&3 |  |  |  |  |  |

| 2:45PM<br>3:00PM      | Coffee Break for Short Course Only Ballroom Foyer                                                |  |  |  |  |  |

| 3:00PM<br>4:30PM      | Compact Modeling of GaN HEMTs Dr. Lan Wei University of Waterloo Studio 2&3                      |  |  |  |  |  |

| 4:30PM<br>4:45PM      | Adjourn and feedback                                                                             |  |  |  |  |  |

|                       | PRIMER  Design methodologies for handheld PAs  Studio 4                                          |  |  |  |  |  |

| 7:30AM<br>12:50P<br>M | Registration for Primer Only Ballroom Foyer                                                      |  |  |  |  |  |

| 8:00AM<br>8:45AM      | Breakfast for Primer Only  Ballroom Foyer                                                        |  |  |  |  |  |

| 8:45AM<br>8:50AM      | Welcome & Speaker Introduction, M Schroter, TU Dresden Studio 4                                  |  |  |  |  |  |

| 8:50AM<br>11:00A<br>M | Primer Lecture - Part 1, Calogero Presti, Kyocera <b>Studio 4</b>                                |  |  |  |  |  |

| 11:00A<br>M<br>11:10A | Coffee Break for Primer Only Ballroom Foyer                                                      |  |  |  |  |  |

| 11:10A<br>M<br>12:40P | Primer Lecture - Part 2, Calogero Presti, Kyocera <b>Studio 4</b>                                |  |  |  |  |  |

| 12:40P<br>M<br>12:50P | Adjourn and feedback                                                                             |  |  |  |  |  |

# 2024 BCICTS SCHEDULE AT A GLANCE

|                    | MONDAY - OCTOR                                              | BER 28                                                         |  |  |

|--------------------|-------------------------------------------------------------|----------------------------------------------------------------|--|--|

| 7:30AM<br>5:00PM   | Registration/Continental Breakfast Foyer                    |                                                                |  |  |

| 8:30AM<br>9:00AM   | Welcome and Announcements <b>Ballroom</b>                   |                                                                |  |  |

| 9:00AM<br>9:40AM   | Plenary Session 1  Ballroom                                 |                                                                |  |  |

| 9:40AM<br>10:20AM  | Plenary Session 2<br>Ballroom                               |                                                                |  |  |

| 10:20AM<br>10:50AM | Sponsored Coffee Break – <b>Qorvo</b> BALLROOM FOYER        |                                                                |  |  |

| 10:40AM<br>12:20PM | 1a. Advances in Physics-<br>Based HEMT Modeling<br>Ballroom | 1b. mmW Mixers and<br>Downconverters<br>Studio 2,3,4           |  |  |

| 12:20PM<br>1:50PM  | Lunch Break Self-Arrangement                                |                                                                |  |  |

| 1:50PM<br>3:30PM   | 2a. Applications of III-V<br>Device Modeling<br>Ballroom    | 2b. mmW & THz<br>Transceiver Technology<br><b>Studio 2,3,4</b> |  |  |

| 3:30PM<br>4:00PM   | Sponsored Coffee Break – Texas Instrument Ballroom Foyer    |                                                                |  |  |

| 4:00PM<br>5:20PM   | 3a. High Voltage, high performance WBG devices Ballroom     | 3b. Ku-Band and Satellite<br>Circuits<br>Studio 2,3,4          |  |  |

| 5:30PM<br>7:30PM   | Exhibition Reception  Ballroom Foyer                        |                                                                |  |  |

|                                                                                      | TUESDAY – OCTOBER 29                                |                                                                |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------|--|--|--|--|--|--|

| 7:30AM<br>5:00PM                                                                     | Registration<br><b>Foyer</b>                        |                                                                |  |  |  |  |  |  |

| 7:30AM<br>8:30AM                                                                     | Exhibition Breakfast  Ballroom Foyer                |                                                                |  |  |  |  |  |  |

| 8:30AM<br>2:30PM                                                                     | Exhibition<br>Ballroom Foyer                        |                                                                |  |  |  |  |  |  |

| 8:30AM                                                                               | 4a1. SiGe Technology and Modeling Ballroom          | 4b. High-Performance<br>Circuits for Optical<br>Communications |  |  |  |  |  |  |

| 10:30AM                                                                              | 4a2. RF Reliability and TCAD to Circuits Ballroom   | Studio 2,3,4                                                   |  |  |  |  |  |  |

| 10:30AM<br>10:50AM                                                                   | Coffee Break Ballroom Foyer                         |                                                                |  |  |  |  |  |  |

| 5a. Advanced Alloys ar<br>10:50AM Architectures for GaN<br>12:10AM HEMTs<br>Ballroom |                                                     | 5b. Low Noise Amplifiers for mmW Applications Studio 2,3,4     |  |  |  |  |  |  |

| 12:10PM<br>1:40PM                                                                    | Exhibition Lunch Ballroom Foyer                     |                                                                |  |  |  |  |  |  |

| 1:40PM<br>3:20PM                                                                     | 6a. Advanced SiGe<br>Process Technology<br>Ballroom | 6b. Novel mmW Devices & Design Techniques Studio 2,3,4         |  |  |  |  |  |  |

| 3:20PM<br>3:40PM                                                                     | Coffee Break Ballroom Foyer                         |                                                                |  |  |  |  |  |  |

| 3:40PM<br>5:20PM                                                                     | 7a. III-V Power Amplifiers  Ballroom                | 7b. Analog ICs<br>Studio 2,3,4                                 |  |  |  |  |  |  |

# 2024 BCICTS SCHEDULE AT A GLANCE

|                            | WEDNESDAY – OCTOBER 30                                                   |                                                                   |  |  |  |  |  |

|----------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------|--|--|--|--|--|

| 7:30AM<br>3:30PM           | Registration/Continental Breakfast  Foyer                                |                                                                   |  |  |  |  |  |

| 8:30AM<br>10:10A<br>M      | 8a. Reliability and physics of Si/SiGe bipolars  Ballroom                | 8b. mmW Metrology & Power<br>Amplifier Technology<br>Studio 2,3,4 |  |  |  |  |  |

| 10:10A<br>M<br>10:30A      | Sponsored Coffee Break – Global Foundries  Ballroom Foyer                |                                                                   |  |  |  |  |  |

| 10:30A<br>M<br>11:30A<br>M | 9a. Diamond and Novel III-V<br>Designs for High Power<br><b>Ballroom</b> | 9b. Receiver Circuits<br>Studio 2,3,4                             |  |  |  |  |  |

| 11:30A<br>M<br>1:00PM      | Lunch Self-Arrangement                                                   |                                                                   |  |  |  |  |  |

| 1:00PM<br>2:40PM           | 10. Late News<br>Ballroom                                                |                                                                   |  |  |  |  |  |

| 2:40PM<br>3:10PM           | Closing Session <b>Ballroom</b>                                          |                                                                   |  |  |  |  |  |

| 3:10PM<br>4:00PM           | Reception Ballroom Foyer                                                 |                                                                   |  |  |  |  |  |

# ADDITIONAL INFORMATION

**REGISTRATION** Complete registration information is contained in the centerfold of this booklet as well as on the conference's web page (<a href="https://bcicts.org">https://bcicts.org</a>) Please use the website to register. The advanced registration deadline is **September 13**. All conference activities are included in the registration fees (technical sessions, coffee breaks, Monday exhibition reception, Tuesday exhibition breakfast and Wednesday lunch

**CONFERENCE SOCIAL EVENTS** Several events have been arranged to promote informal social interactions among conference participants.

**TUTORIAL / SURVEY TALKS** Tutorial talks given by invited experts are intended to give a broad overview of a given subject with a critical review of technology and applications. They are twice the length of the usual contributed talk with longer abstracts in the Proceedings.

**MEMBERS OF THE PRESS:** You are welcome to attend BCICTS. Admission is free. Please email Catherine Shaw, CMP, Executive Conference Director at: <a href="mailto:cs@cshawevents.com">cs@cshawevents.com</a> for pre-registration and approval by our Executive Committee.

**RECRUITING:** intensive recruiting undermines the purposes for which the BCICTS was established and is contrary to IEEE policy.

# **BEST STUDENT PAPER AND BEST PAPER AWARDS**

BCICTS offers a Best Paper Award. The BCICTS Best Paper Award recognizes and promotes high quality contributions to scholarly research among professionals who author and present papers at the conference. All papers submitted in non-student category are eligible for consideration for the Best Paper Award.

The BCICTS Best Student Paper Award recognizes and promotes outstanding research led by students. The Best Student Paper Award the following criteria: 1) the student must have carried out a substantial part of the research reported in the paper, 2) the student must be the first author and must present the paper at the conference, 3) the paper must be identified as a student paper during submission of the paper.

Eligible papers have been evaluated by the Best Paper Award Committee and the notifications will be sent out after the conference.

### **OUR SPONSORS**

BCICTS is sponsored by the IEEE Electron Devices Society (EDS) in co - operation with the IEEE Solid - State Circuits Society (SSCS) and the IEEE Microwave Theory & Techniques Society (MTT).

# MEETINGS & SESSIONS SCHEDULE DETAILS

# SUNDAY

# BCICTS 2024 SHORT COURSE Studio 2&3

- Dr. Edwin L. Piner (Texas State University)

- Dr. Jose Jimenez (Qorvo)

- Dr. Markus Müller (TU Dresden, Rohde & Schwarz)

- Dr. Lan Wei (University of Waterloo)

# 8:00-8:45 AM Breakfast (Primer/Short Course Only)

8:45 – 8:50 AM - Welcome & Speaker Introduction Doug Weiser, Texas Instruments

# 8:50 – 10:20 AM – III-V Epitaxial & Thin Film Deposition, Processes and Opportunities

Instructor: Dr. Edwin L. Piner, Texas State University

Abstract: Epitaxial and thin film formation processes on single-crystal semiconductor substrates directly enable the various elaborate III-V heterojunction device designs and, therefore, dictate the resulting electronic or optoelectronic device performance. The III-V heterojunction comprises not only the concept of varying dopant species across the junction, but more importantly, also varying the semiconductor crystals and thereby differentiates III-V device design options and concomitant performance benefits over silicon-based devices. The earliest commercially viable example is the AlGaAs/GaAs junction which exploits the energy bandgap difference to engineer charge carrier confinement. GaAs has a narrower bandgap than AlGaAs, and the AlGaAs bandgap may be 'tuned' by precisely controlling the Al composition. Several decades of research have led to the development of III-V heterojunction compounds across the entire semiconductor spectrum; B-, Al-, Ga- and In- from column-III, with N-, P-, As-, and Sbfrom column-V of the periodic table. This presentation will delve into the topics of III-V epitaxy and thin film deposition techniques, key process considerations, heterojunction challenges and limitations, and offer perspectives on future opportunities.

Edwin L. Piner received his Ph.D. in Material Science and Engineering from North Carolina State University in 1998. He held multiple research & development related positions in industry beginning with ATMI Corp., Epitronics division in Phoenix, AZ, then with Nitronex Corp. in Durham, NC. In 2010 he joined Texas State University's Physics department, coinciding with the launch of the Materials Science, Engineering & Commercialization Ph.D. program where he attained tenure and promotion to Professor in 2013. In addition to his Texas State faculty appointment, Dr. Piner is Chair of the Physics Department. Dr. Piner has numerous publications in the areas of wide- and ultra-wide bandgap materials and devices, is inventor on 33 US patents, and is a member of MRS, ECS and senior member of IEEE.

# 10:35 - 12:05 PM GaN Process and Reliability

Instructor: Dr. Jose Jimenez, Qorvo

Abstract: This short course will cover two important aspects of GaN RF Transistor Technology: Device Fabrication and Reliability. On the fabrication section, we will start describing a standard GaN FET process flow, highlighting the differences with its cousin the standard GaAs FET flow. We will cover modules such as ohmics, gate formation, semiconductor passivation, passives and Vias and discuss alternatives within each module. Once the process modules are introduced, we will discuss their main challenges not from the process perspective, but on how they affect the device performance. We will wrap up this section, discussing the challenges and opportunities of improvements as GaN technology moves to nodes designed to cover a higher frequency space or with higher linearity requirements. If time permits, we will cover additional process challenges on alternative sister GaN technologies such as GaN nPolar, GaN Fins, etc .... On the reliability section, we will cover the history behind the intrinsic GaN reliability failure modes, starting with the inverse piezoelectric effect and ending with the chemical reactions responsible for the formation of pitting. In this section, we will also discuss other non-GaN intrinsic failure modes. Though not intrinsic to the GaN material, they have limited the reliability span of the GaN technology. Finally, if time permits, we will attack the challenges of assessing GaN reliability. Though this could seem off topic, it is an essential part of establishing GaN reliability, given the large self-heating and fields the devices are subjected to during operation.

Jose Jimenez is a Sr. R&D Fellow at Qorvo. He received the B.A (1992) in Electrical Engineering from the Universidad Politecnica de Madrid and the Ph. D. (1996) in Electrical Engineering from Columbia University in New York. He is also a La Caixa Fellow and a Beckman Fellow. Jose Jimenez started his professional career working in integrated optics and optoelectronics in Telefonica R&D (Spain), T. J. Watson IBM Research Laboratory, Beckman Institute and Nanovation Technologies. For the last 23 years, he has been part of the R&D organization of TriQuint Semiconductor (Qorvo now) originally leading the efforts first in 4" inch optoelectronics devices (DFB lasers and high speed photo-detectors) and later in GaN FETs. He holds 15 patents and has written more than 100 articles. He is currently a technical committee emeritus chair for the RF/5G/ mmW chapter of the International Reliability Physics Symposium, and a committee member of the European Symposium on Reliability of Electron Devices and the Microwave Theory & Technique Society. At Qorvo, Jose is a member of the GaN technology steering and patent Committees.

# 12:05 - 1:15 PM Lunch

# 1:15 - 2:45 PM

**Device and Compact Modeling of InP HBTs**

Instructor: Dr. Markus Müller, TU Dresden, Rohde & Schwarz

**Abstract:** High-speed Heterojunction Bipolar Transistors (HBTs) based on III-V semiconductors are highly favorable for mm-wave and sub-mm-wave applications due to their high transconductance, transit frequency ( $f_T$ ), and maximum oscillation frequency (fmax). The most advanced technologies achieve ultra-high  $f_T > 500$  GHz and fmax >

1 THz, but compact and TCAD modeling for these technologies lag behind those for SiGe, necessitating further research. This lecture begins with a review of the most advanced high-speed InP HBTs and their experimental characterization. It will then compare competing III-V HBT technologies based on the InP/GaAsSb and InP/InGaAs material systems. Following this, a review of available compact models and critical effects will be provided, highlighting phenomena such as self-heating, non-quasistatic (NQS) effects, and negative differential mobility (NDM) effects. A high-level overview of the parameter extraction process will be given. Subsequently, the necessary physics and material parameters for TCAD simulation of III-V HBTs will be detailed, along with exemplary results. The session will conclude by highlighting open questions in the field.

Markus Müller earned his Master's in Electrical Engineering in 2019, followed by a Ph.D. in 2024, both from TU Dresden. In 2024, he joined Rohde & Schwarz as a device engineer in the MMIC group. His work focuses on III-V semiconductor compact and TCAD modeling, with several publications in high-impact journals. Additionally, Markus co-founded SemiMod GmbH, where he contributed to the extraction of scalable HICUM/L2 libraries for some of the world's most advanced SiGe HBT technologies.

# 2:45 - 3:00 PM - Coffee Break

# 3:00 – 4:30 PM – Compact Modeling of GaN HEMTs Instructor: Dr. Lan Wei, University of Waterloo

**Abstract:** With the maturing and commercial rollout of Gallium-nitride (GaN) technology, compact modeling has become an essential part of the GaN design and manufacturing ecosystem. In this short course, we start with a brief introduction of the GaN HEMT technology and the needs of compact modeling, and then discuss the general requirements for compact model and challenges for GaN modeling. A few different approaches of compact modeling will also be compared, followed by a brief introduction of the physics-based MVSG GaN HEMT compact model.

Lan Wei received her B.S. in Microelectronics from Peking University, China (2001), M.S and Ph. D. in Electrical Engineering from Stanford University, USA (2007 and 2010, respectively). She worked as a Postdoc Associate in MIT from 2010-2012 and as a Member of Technical Staff with Altera Corporation from 2012-2014. She joined University of Waterloo, Canada, in 2014, where she is currently Associate Professor. Prof. Wei has intensive experience in device physics-based compact modeling including silicon and GaN technologies, device-circuit interactive design and optimization, integrated nanoelectronic systems with lowdimensional materials, cryogenic CMOS device modeling and circuit design for quantum computing. She was listed as one of the key contributors to the Process Integration, Devices, and Structures Chapter (PIDS) of International Technology Roadmap for Semiconductors (ITRS) 2009 Edition. She is the co-developer of the MIT Virtual Source GaN HEMT (MVSG) Compact Model, which is an Industry Standard approved and supported by the Compact Model Coalition for GaN HEMT compact model. She has authored/co-authored more than 100 peered reviewed publications and served on the technical program committees including IEDM, ICCAD, DATE, ISQED, and BCICTS etc.

# **BCICTS 2024 PRIMER**

Studio 4

**Date:** Sunday, October 27, 2024 **Time:** 8:00 AM – 12:50 PM

**Topic:** Design methodologies for handheld PAs

Instructor: Calogero Presti, Senior Principal Engineer, RFIC

Design at Kyocera — Lecturer at UCSD (Power

Amps.)

8:00 – 8:45 AM Breakfast

8:45 – 8:50 AM Welcome - Michael Schröter

8:50 – 11:00 AM Primer Lecture – P1 - Calogero Presti

11:00 - 11:10 AMCoffee Break

11:10 - 12:40 PMPrimer Lecture - P2 - Calogero Presti

12:40 - 12:50 PM Adjourn and Feedback

The primer course is an introductory-level course on a selected topic relevant to BCICTS attendees.

### Abstract:

In this course, we will delve into the fascinating world of RF power amplifiers (PAs). These essential components play a crucial role in radio transmitters and communication systems. Whether you're a seasoned engineer or just starting out, this session promises valuable insights into the heart of wireless communication.

We'll begin by reviewing the foundational characteristics of modulated signals. Understanding these properties is essential for designing efficient PAs. Signal fidelity, linearity, and distortion will be explored in the context of PA design. We will then dwell into classic PA Theory. Using an idealized transistor model, we'll develop intuition about critical PA concepts, such as loadline tuning (how to optimize the loadline for maximum power delivery), harmonic termination, strategies to improve efficiency, and the definition of the canonical Amplifier Classes (A, B, AB, C). We'll discuss the pros and cons of each amplifier class and their real-world applications.

Then we will approach Practical PA design. We will discuss Class F and J matching topologies, exploring matching networks and efficiency considerations related to second harmonic termination. Then a sample GaAs HBT PA Design will be developed. We will apply theoretical concepts to design a 2-stage PA using a simplified GaAs HBT model. Finally an overview of advanced efficiency enhancement techniques will be given: Doherty and Envelope Tracking. Join us for an engaging exploration of RF power amplifiers, where theory meets practical design. By the end of this primer, you'll be well-equipped to tackle real-world challenges in RF PA design and optimization.

Calogero D. Presti received the Ph.D. degree in electronics and automation engineering from the University of Catania, Italy, in 2008, working on CMOS Power Amplifiers and Silicon Photonics. During 2009 he was a postdoctoral researcher at UC San Diego, mainly working on PA digital predistortion and envelope tracking. In 2010 he joined Qualcomm Inc., San Diego, CA, where he was part of the team that started the RF Front-End business in the company. There he designed several CMOS and GaAs PAs, and led some front-end module integration for sub-6GHz cellular applications. In 2019 he joined IDT (now part of Renesas) where he designed all the PAs used in mm-Wave beamformers (cellular, satcom, and radar) and occasionally supported the sub-6GHz businesses. Recently, he joined Kyocera, where he designs mm-wave power amplifiers for 5G infrastructure.

Since 2017 he teaches the Power Amplifier design class at UC San Diego.

# **MONDAY**

# INTRODUCTORY REMARKS AND PLENARY

# WELCOME AND ANNOUNCEMENTS Monday, 8:30 - 9:00 AM Ballroom Tomislav Suligoj, Symposium Chair

# PLENARY 1

Monday 9:00 AM – 9:40 AM *Ballroom*

Session Chair: Tomislav Suligoj, *University of Zagreb*Co-chair: Michael Roberg, *Qorvo*

# Review of DARPA's T-Music Program

Todd Bauer

DARPA Microsystems Technology Office

# PLENARY 2

Monday 9:40 AM – 10:20 AM *Ballroom*

Session Chair: Michael Roberg, *Qorvo* Co-chair: Tomislav Suligoj, *University of Zagreb*

The European Chips Act

Yves Gigase Chips Joint Undertaking

# CONFERENCE PROGRAM

# 1a. Advances in Physics-Based HEMT Modeling

Monday 10:40 AM Ballroom

Session Chair: Lei Zhang, NXP Semiconductors

Co-Chair: Subrata Halder, Qorvo

# 1a.1 (Invited)

# 10:40-11:20 AM - A Family of Physics-Based Models for Monolithic GaN Integration

Lan Wei1, Ryan Fang1, Yijing Feng1, Johan Alant1, Ujwal Radhakrishna2

1 Department of Electrical and Computer Engineering,

University of Waterloo, Waterloo, Canada 2 Kilby Research Labs, Texas Instruments Inc., Santa Clara, United States

# 1a.2 (student)

# 11:20-11:40 AM - Physics-Based Compact Model for GaN-Based Non-linear Transmission Line Resistors

Johan Alant1, Ryan Fang1, Yuxuan Zhang2, Pilsoon Choi3, Yijing Feng1, Jessica Chong1, Zev Pogrebin2, Bin Lu2,

Ujwal Radhakrishna4, Lan Wei1

1University of Waterloo, Waterloo, Canada 2Finwave Semiconductor, Waltham, United States

3Massachusetts Institute of Technology, Cambridge, United States

4Texas Instruments, Santa Clara, United States

# 1a.3 (student)

# 11:40-12:00 PM - A Hybrid Physical ASM-HEMT Model Using a Neural Network-Based Methodology

Rafael Perez Martinez1, Masaya Iwamoto2, Ana M. Banzer Morgado1, Yiao Li2, Roberto Tinti3,

Jianjun Xu2, Chad Gillease2, Steven Cochran2, Bhawani

Shankar1, Else-Marie Schmidt2, Zijian Song3, Natalie Wagner2, Philipp Pahl2, Alexander

Petr3, and Srabanti Chowdhury1

1 Department of Electrical Engineering, Stanford University, Stanford, CA USA

2Keysight Technologies Inc., Santa Rosa, CA USA 3Keysight Technologies Inc., Calabasas, CA USA

# 12:00-12:20 PM - Large-Signal Modeling of a 50 nm mHEMT Incorporating a Physical Impact-Ionization Model

Yasin Yüce, Sayed Ali Albahrani, Dirk Schwantuschke, Arnulf Leuther

Fraunhofer Institute for Applied Solid State Physics (IAF), Freiburg, Germany

# 1b. mmW Mixers and Downconverters

Monday 10:40 AM Studio 2.3.4

Session Chair: Daniel Dong, Samsung Research America

Co-Chair: Wooram Lee, Penn State University

# 1b.1 (Invited)

# 10:40-11:20 AM - N-Path Mixers Beyond CMOS

Alyosha Molnar

Cornell University, Ithaca, NY, USA

# 1b.2

# 11:20-11:40 AM - W-band GaN Resistive FET I-Q Mixer **MMICs with Low Conversion Loss**

Daniel Kuzmenko<sup>1</sup>, Harris Moyer<sup>1</sup>, Jana Georgieva<sup>1</sup>, Tai Haw<sup>1</sup>, Stephen A. Maas<sup>2</sup>

1HRL Laboratories, LLC, Malibu, CA, USA

<sup>2</sup>Nonlinear Technologies, Inc., Long Beach, CA, USA

11:40-12:00 AM - A D-band SiGe Subharmonic **Downconverter with Dynamic Conversion Gain and Fixed Input Compression**

Jonathan Tao, James F. Buckwalter

Department of Electrical and Computer Engineering, University of California, Santa Barbara, CA, USA.

12:00-12:20 AM - A Sub-Sampling 35GHz PLL in 45nm PDSOI BiCMOS with 37fs Integrated Jitter and a FoM of

Christopher Chen, Yan Zhang, Hao-Yu Chien, Jiazhang Song, Jia Zhou, Chao-Jen Tien, Sudhakar Pamarti, Chih-Kong Ken Yang, Mau-Chung Frank Chang Department of Electrical and Computer Engineering, University of California, Los Angeles, CA, USA

# 2a. Applications of III-V Device Modeling

Monday 1:50 PM Ballroom Session Chair: John Robert Jones, BAE Systems, Inc. Co-Chair: Masaya Iwamoto, Keysight Technologies

2a.1 (Invited) 1:50-2:30 PM - Practical dimensions of contemporary

GaN modeling Larry Dunleavy, Jiang Liu and Hugo Morales Modelithics, Inc., USA

# 2a.2 (student)

-252dB

2:30-2:50 PM - ASM-GaN Model for Resistive Mixer Applications at D-Band Frequencies

Cristina Maurette-Blasini1, Dirk Schwantuschke2, Sayed Ali Albahrani2, Peter Brückner2,

Konstantin Kuliabin1, Sébastien Chartier2, Rüdiger Quay1 1Institute for Sustainable Systems Engineering (INATECH), University of Freiburg, Germany 2Fraunhofer Institute of Applied-Solid-State Physics (IAF),

Germany

2:50-3:10 PM - Characterization and Large-Signal Modeling of 4-Pole Backgated InGaAs HEMT Antony Abel Kunnath, Sayed Ali Albahrani, Dirk Schwantuschke, Arnulf Leuther

Fraunhofer IAF, Freiburg, Germany

## 2a.4 (student)

2a.3

3:10-3:30 PM - Small-Signal Model Verification and Analysis of Unmatched Multi-Finger HBT Cells at 220

Rob D. Jones1,2, Jerome Cheron1,3, Benjamin F. Jamroz1, Ari D. Feldman1, and Peter H. Aaen2

1 National Institute of Standards and Technology (NIST), Boulder, CO 80305

2 Colorado School of Mines, Golden, CO 80401

3 Department of Physics, University of Colorado, Boulder CO 80309

# 2b. mmW & THz Transceiver Technology

Monday 1:50 PM Studio 2.3.4 Session Chair: Marcus Pan, Semiconductor Research Corporation

Co-Chair: Kazuya Yamamoto, Mitsubishi Electric Corporation

# 2b.1 (Invited)

1:50-2:30 PM - 300-GHz-Band InP HBT Power Amplifier and InP-CMOS Hybrid Phased-Array Transmitter T. Jyo1, I. Abdo1, H. Hamada1, M. Nagatani1, A. Pander1, H.

Wakita<sup>1</sup>, M. Mutoh<sup>1</sup>, Y. Shiratori<sup>1</sup>, D. Kitayama<sup>1</sup>, C. D. Gomez<sup>2</sup>, C. Wang<sup>2</sup>, K. Hatano<sup>2</sup>, C. Liu<sup>2</sup>, A. A. Fadila<sup>2</sup>, J. Pang<sup>2</sup>, A. Shirane<sup>2</sup>, K. Okada<sup>2</sup>, H. Takahashi<sup>1</sup>

<sup>1</sup> NTT Device Technology Labs, NTT Corporation, Kanagawa,

<sup>2</sup>Tokyo Institute of Technology, Tokyo, Japan

2b.2

2:30-2:50 PM - 300-GHz 160-Gb/s InP-HEMT Wireless

Front-End with Fully Differential Architecture H. Hamada<sup>1</sup>, I. Abdo<sup>1</sup>, T. Tsutsumi<sup>2</sup>, H. Takahashi<sup>1</sup>

<sup>1</sup>NTT Device Technology Labs, NTT Corporation, Kanagawa, Japan <sup>2</sup>Department of Physics and Electronics, Osaka Metropolitan

University, Osaka, Japan

2b.3 2:50-3:10 PM - A Q-band Phased-Array Transmit Beamformer in 45nm CMOS SOI for SATCOM

T. Ren, Y. Chang, B. A. Floyd

North Carolina State University, Raleigh, NC, USA

2b.4

# 3:10-3:30 PM -Full Antenna in Package Solution for 100GHz 6G infrastructure, in 140nm SiGe BiCMOS Technology

P.H.C. Magnée<sup>1</sup>, R. Mandamparambil<sup>1</sup>, P. Mattheijssen<sup>1</sup>, M.

Acar<sup>1</sup>, K. Giannakidis<sup>1</sup>, X. Yang<sup>1</sup>, Z. Chen<sup>1</sup>, P. Freidl<sup>1</sup>, J.J.T.M. Donkers<sup>1</sup>, P.G.M. Sebel<sup>1</sup>, I. Brunets<sup>1</sup>, J.W. Bergman<sup>1</sup>, D. Leenaerts<sup>1</sup>, A. Ghannam<sup>2</sup>, S. Danielsson<sup>1</sup>, G. Bisht<sup>3</sup>, M. Lal<sup>3</sup>, W.-C. Liao4, O. Tageman4

<sup>1</sup>NXP Semiconductors, Eindhoven, Netherlands <sup>2</sup>3DiS Technologies SAS, Labège, France <sup>3</sup>Systems on Silicon Manufacturing Company, Singapore

3a. High Voltage, high performance WBG devices Monday 4:00 PM Ballroom

Session Chair: Martin Claus, Infineon Co-Chair: Vibhor Jain, GlobalFoundries

<sup>4</sup>Ericsson Research, Stockholm, Sweden

3a.1 (Invited) 4:00-4:40 PM - SiC High-Voltage Power Devices and **High-Temperature ICs**

T. Kimoto, M. Kaneko, K. Tachiki, K. Ito, K. Mikami, H. Fujii, A. Inoue, R. Ito, and N. Maeda Department of Electronic Science and Engineering, Kyoto

University

# 4:40-5:00 PM - High-Temperature Stability Base Ohmic Contacts for InP/GaAsSb DHBTs

F. Ciabattini, A. M. Arabhavi, S. Hamzeloui, G. Bonomo, M. Ebrahimi, O. Ostinelli and C. R. Bolognesi Millimeter-Wave Electronics (MWE) Group, ETH-Zürich

# 3b. Ku-Band and Satellite Circuits

Monday 4:00 PM Studio 2.3.4 Session Chair: Michael Litchfield, BAE Systems

# Co-Chair: Farooq Amin, Northrop Grumman

3a.2 (Student)

3b.1 (Invited) 4:00-4:40 PM - III-V Semiconductors in Commercial

Communication Satellite Payloads Jim Sowers

Maxar Space Infrastructure, Sunnyvale, CA, USA

3b.2

4:40-5:00 PM - A Ku-Band SiGe:C Power Amplifier with 24.8 dBm Output Power and 35.6% Peak PAE

Christian Bredendiek<sup>1</sup>, Jan Wessel<sup>1</sup>, Klaus Aufinger<sup>2</sup>, Nils Pohl1,3

<sup>1</sup> Fraunhofer FHR, Fraunhofer Institute for High Frequency Physics and Radar Techniques FHR, Wachtberg, Germany

<sup>2</sup> Infineon Technologies AG, Neubiberg, Germany <sup>3</sup> Institute of Integrated Systems, Ruhr-University Bochum,

Germany

5:00-5:20 PM - A compact low-loss Ku-Band 90° Hybrid Coupler for Front-End Modules in 45 nm SOI CMOS Evgenii Fedorov and Vadim Issakov CMOS Design, TU Braunschweig, Institute for

Braunschweig, Germany

3b.3

# TUESDAY

# 4a1. SiGe Technology and Modeling

Tuesday 8:30 AM Ballroom

Session Chair: Breandán Ó hAnnaidh, Analog Devices

Co-Chair: Michael Schroter, TU Dresden

### 4a1.1 (Invited)

08:30-9:10 AM - SiGe BiCMOS or FET Technologies for Wireless PA Applications

Randy Wolf, Shafi Syed, Abdellatif Bellaouar, Chi Zhang, Vibhor Jain, Rebouh Benelbar, Sujata Ghosh, Vivek Tamarkar.

GlobalFoundries – Essex Junction, VT, USA

GlobalFoundries – Dallas, TX, USA

GlobalFoundries - Malta, NY, USA

GlobalFoundries - Bengaluru, India

# 4a1.2 (Student)

# 9:10-9:30 AM - Systematic Extraction of Thermal

Network Parameters in Multi-Finger SiGe HBTs

Sovan Barman, Subham Pande, Suresh Balenethiram,

Thomas Zimmer, Sebastien Fregonese, and Anjan Chakravorty

Indian Institute of Technology, Madras, Chennai, India National Institute of Technology Puducherry, Karaikal, India IMS Laboratory, University of Bordeaux, France

# 4a2. RF Reliability and TCAD to Circuits

Tuesday 9:30 AM Ballroom

Session Chair: Pete Zampardi, Qorvo Co-Chair: Saurabh Sirohi, GlobalFoundries

### 4a2.1 (Invited)

# 9:30-10:10 AM - TCAD for Circuits and Cells: Process **Emulation, Parasitics Extraction, Self-Heating**Z. Stanojevic, X. Klemenschits, G. Rzepa, F. Mitterbauer, C.

Schleich, F. Schanovsky, O. Baumgartner, and M. Karner.

Global TCAD Solutions GmbH, Vienna, Austria

### 4a2.2

# 10:10-10:30 AM - On the Safe Operating Area of InP **HBTs**

Markus Muller, Sebastien Fregonese, Christoph Weimer, Guangsheng Liang, Xiaodi Jin, Maximilian Froitzheim, Thomas Zimmer, and Michael Schroter.

TU Dresden, Germany

IMS Laboratory, CNRS, University of Bordeaux, France

# 4b. High-Performance Circuits for Optical <u>Communications</u>

Monday 8:30 AM Studio 2.3.4

Session Chair: Munehiko Nagatani, NTT Corporation Co-Chair: Sorin Voinigescu, University of Toronto

### 4b.1 (Invited)

8:30-9:10 AM - 800 Gpbs Coherent Optical Sub-Assembly (COSA) based on Coupling Modulator Silicon Ring Resonator

A. Rylyakov

Nokia of America Corporation

# 4b.2 (Invited)

9:10-9:50 AM - Integrated Photonics in Thin-Film Lithium Niobate

C. Reimer

HyperLight

### 4b.3

9:50-10:10 AM - Broadband Linear Drivers for 800G/1.6T **Energy Efficient Optical Links**

M. Hahmud, Hal-Rubaye\*, G. Rebeiz

<sup>1</sup> University of California San Diego \*Now at Broadcom, Inc.

### 4b.4

10:10-10:30 AM - A 64Gb/s Si-Photonic Micro-Ring Resonator Transceiver with Co-designed CMOS Driver and TIA for WDM Optical-IO

Qianli Ma<sup>1,3</sup> Sikai Chen<sup>1</sup>, Jintao Xue<sup>2,3</sup>, Yingjie Ma<sup>1,3</sup>, Yuean Gu³, Chao Cheng²,³, Yihan Chen³, Haoran Yin¹,³, Guike Li¹,³, Zhao Zhang¹,³, Nanjian Wu¹,³, Ke Li⁴, Lei Wang⁴, Ming Li¹,³, Chao Xiang⁵, Binhao Wang²,³, Nan Qi¹,³\*, Liyuan Liu¹,³ <sup>1</sup>Institute of Semiconductors, Chinese Academy of Sciences, Beijing, China,

<sup>2</sup>Xi'an Institute of Optics and Precision Mechanics. Chinese Academy of Sciences, Xi'an, China,

<sup>3</sup>University of Chinese Academy of Sciences, Beijing, China, <sup>4</sup>Peng Cheng Laboratory, Shenzhen, China,

5The University of Hong Kong, Hong Kong, China

# 5a. Low Noise Amplifiers for mmW Applications

Tuesday 10:50 AM Ballroom Session Chair: Akshay Visweswaran, Nokia Bell Labs Co-Chair: Ignacio Ramos, HRL Laboratories, LLC.

# 5a.1

10:50-11:10 AM - A 200-250 GHz Low-Noise Amplifier in 130-nm InP HBT with 15.5 dB Gain and Record 5.3 dB Noise-Figure at 212 GHz

Amirreza Alizadeh#1, Kwangwon Park#2, Saleh Hassanzadehyamchi\$3,

Utku Soylu#4, Miguel E. Urtega\*5, Mark J.W. Rodwell#6 #University of California, Santa Barbara, CA, USA \$University of California, Davis, CA, USA \*Teledyne Scientific, Thousand Oaks, CA, USA

# 5a.2

11:10-11:30 AM - A 7.7-mW DC-to-62 GHz Ultra-Wideband Low-Noise Amplifier with ±2.1 ps Group Delay Variation and 3.3 dB NF in 0.13-mm SiGe:C BiCMOS

Eren Vardarli#, Austin Ying-Kuang Chen\$, Michael Schroter# #TU Dresden, Germany

\$University of California, Santa Cruz, USA

# 5a.3

# 11:30-11:50 AM - A Biasing Scheme for the Gain Compression Point Optimization of HBT Cascode D-**Band LNAs**

Lorenzo Serra, Guglielmo De Filippi, Lorenzo Piotto, Andrea Mazzanti

University of Pavia, Italy

# 11:50 AM-12:10 PM - A 5.6 dB NF Two-Stage 110 - 125 GHz LNA Gain-Boosted by RC-over-Neutralization for Radar Applications in 28 nm CMOS

V. Lasserre<sup>1</sup>, S. Koop-Brinkmann<sup>1</sup>, M. Caruso<sup>2</sup>, D. Dal Maistro<sup>2</sup>, G. Volpato<sup>2</sup>, Q. H. Le<sup>3</sup>, T. Kämpfe<sup>3</sup>,

C. Ziegler<sup>1</sup>, F. Stapelfeldt<sup>1</sup>, V. Issakov<sup>1</sup>

<sup>1</sup>Braunschweig University of Technology, Germany

<sup>2</sup>Infineon Austria, Villach, Austria

<sup>3</sup>Fraunhofer Institute for Photonic Microsystems, Dresden, Germany

# 5b. Advanced Alloys and Architectures for GaN HEMTs Tuesday 10:50 AM *Studio 2.3.4*

Session Chair: Tim Vasen, Northrop Grumman Co-Chair: Ken Kikuchi, Sumitomo Electric

# 5b.1 (Invited)

10:50-11:30 AM - Characterization of ScAIN/GaN Toward **Electronic Device Application**

T. Maeda<sup>1</sup>, Y. Wakamoto<sup>1</sup>, and A. Kobayashi<sup>2</sup> <sup>1</sup>University of Tokyo, Tokyo Japan, <sup>2</sup>Tokyo University of Science, Tokyo, Japan 11:30-11:50 AM – Performance Limitations of GaN HEMTs with Quaternary InAlGaN and ScAlGaN Barrier Layers

I. Berdalovic, D. Novakovic, and T. Suligoj

University of Zagreh, Zagreh, Croatia

University of Zagreb, Zagreb, Croatia

5b.3 11:50 AM-12:10 PM – Design kit development on a 300mm GaN-on-Si demonstration platform with

integrated Si pMOS

S. J. Bader1, A Zubair, A. Latorre-Rey, M. Hansen, S. Sarkar, A. Asif, D. Frolov, K. Narayanan, J. Rangaswamy, P. K. Kaur, S. Kumar, N. Kundu, S. S. Jayanrakash, A. Khobragade, P.

S. Kumar, N. Kundu, S. Ś. Jayaprakash, A. Khobragade, P. Yashwanth, Q. Yu, J. Vasudevan, I. Momson, S. Rami, H. Vora, M. Radosavljevic, P. Koirala, M. Beumer, A. Vyatskikh, P. Nordeen, T. Hoff, N. Desai, and H. W. Then

# 6a. Advanced SiGe Process Technology

Intel Corporation, Hillsboro, OR, USA

Tuesday 1:40 PM *Ballroom*Session Chair: Stan Phillips, *Tower Semiconductor*Co-Chair: Jack Pekarik, *GlobalFoundries*

6a.1 (Invited)

1:40-2:20 PM – A Versatile 55-nm SiGe BiCMOS Technology for Wired, Wireless, and Satcom

Applications

P. Chevalier, F. Cacho, C. Durand, N. Derrier, V. Milon, F. Monsieur, A. Gauthier, H. Audouin, M. Buczko, D. Céli, C. Deglise-Favre, C. Diouf, O. Foissey, M. Hello, N. Guitard, S. Madassamy, S. Ramirez-Ruiz, C. Renard, F. Sonnerat, V. Yon, D. Gloria, G. Waltisporaer

Madassamy, S. Ramirez-Ruiz, C. Renard, F. Sonnerat, V. Yon, D. Gloria, G. Waltisperger STMicroelectronics, Technology & Design Platforms, Crolles, France

2:20-2:40 PM – Towards 500GHz f<sub>MAX</sub> 140nm SiGe BiCMOS Technology for 5G/6G Applications J.P. John<sup>1</sup>, J. Kirchgessner<sup>1</sup>, J.J.T.M. Donkers<sup>1</sup>, P.H.C. Magnée<sup>1</sup>, P.G.M. Sebel<sup>1</sup>, R. Werkman<sup>1</sup>,

G. Anderson<sup>1</sup>, I. Brunets<sup>1</sup>, P.K. Uttwani<sup>2</sup>, Mohamed G. Moinuddin<sup>2</sup>, L. Radic<sup>1</sup>, I. To<sup>1</sup>, T.H. Both<sup>1</sup>

\*\*INXP Semiconductors\*\*

<sup>2</sup>Systems on Silicon Manufacturing Company

6a.3 (Student)

2:40-3:00 PM – High-Performance SiGe Heterojunction

Phototransistor in a Commercial SiGe BiCMOS Platform

for Free-Space Optical Receivers

Mozhgan Hosseinzadeh¹, Milad Frounchi¹, George N.

Tzintzarov¹\*, Jeffrey W. Teng¹, and John D. Cressler¹

¹Georgia Institute of Technology

\*Now at The Aerospace Corporation

\*Now at The Aerospace Corporation

3:00-3:20 PM – Practical Simulation and Test Strategies for Advanced Heterojunction Bipolar Transistors Adam W. DiVergilio GlobalFoundries, Essex Junction

**6b. Novel mmW Devices & Design Techniques** Tuesday 1:40 PM **Studio 2.3.4**

Session Chair: Leonardo Vera, Analog Devices Co-Chair: Harris Moyer, HRL Laboratories, LLC.

6b.1 (Invited)

6a.2

1:40-2:20 PM – D-Band meets FinFET: Fully-Integrated Transmitter and Receiver Architectures for 100+Gb/s Links

Steven Callender, Abhishek Agrawal, Amy Whitcombe, Ritesh Bhat, Stefano Pellerano Intel Labs, Intel Corporation, Hillsboro, OR USA

2:20-2:40 PM – A 132-204 GHz Carrier Storage Frequency

Divider with sub-50 Micro-Watt DC Power

Sidharth Thomas, Benyamin Fallahi Motlagh, Aydin

Babakhani

University of California, Los Angeles, USA

# 6b.3 2:40-3:00 PM – A Novel Approach to Zero $\Omega$ Transmission Line Analysis and Design at W-Band and

**Beyond** Israel Tapia, Eren Vardarli, Ciro Esposito and Michael

Technische Universität Dresden, Germany

# 6b.4

Schröter

3:00-3:20 PM – A 10 Gb/s, 120 GHz Compact and Energy-Efficient Harmonic-OOK (HOOK) Modulator using 90 nm SiGe BiCMOS

Shah Zaib Aslam¹ and Najme Ebrahimi²

¹Department of Electrical and Computer Engineering,

University of Florida, Gainesville, FL, USA

²Department of Electrical and Computer Engineering,

Northeastern University, Boston, MA, USA

# 7a. III-V Power Amplifiers

Tuesday 3:40 PM Ballroom

Session Chair: Kazuya Yamamoto, Mitsubishi Electric Corp.

Co-Chair: David Wohlert, Qorvo

# 7a.1 (Invited)

3:40-4:20 PM – Load-Modulated Balanced Amplifiers for Next-G Wireless Communications

Pingzhu Gong, Jiachen Guo, and Kenle Chen

Pingzhu Gong, Jiachen Guo, and Kenle Chen Department of Electrical and Computer Engineering, University of Central Florida, USA

### 7a 2

4:20-4:40 PM – Ka-Band, Reactively Matched Non-Uniform Distributed Power Amplifier MMICs in GaN-on-SiC

Michael Litchfield, Qin Shen-Schultz, and Bernard Schmanski

BAE Systems, Nashua, NH, USA

7a.3 (Invited) 4:40-5:20 PM - Advances in GaN HEMT and GaN Power **Amplifier Techniques for Base-Stations** Bernhard Grote, David Yu-Ting Wu, Bruce Green, Raphael Holin, David Burdeaux, Philippe Renaud, Humayun Kabir, and Patrick Hu NXP Semiconductors, Chandler, Arizona, USA

# 7b. Analog ICs

Tuesday 3:40 PM Studio 2.3.4 Session Chair: Sri Navaneeth Easwaran, Texas Instruments

Co-Chair: Jack Pekarik, GlobalFoundries

# 7b.1 (Invited) 3:40-4:20 PM - High-Efficiency High-Conversion-Ratio

**Power Delivery Circuits for Computing Applications** Hoi Lee1, Chen Chen1, Weijie Han1, Atul Sudha1,

Navaneeth Easwaran<sup>2</sup> Jin Liu<sup>1</sup> <sup>1</sup> UT Dallas, Texas.

<sup>2</sup> Texas Instruments, Dallas, TX

### 7b.2

# 4:20-4:40 PM - A Single-Stage 24 Gb/s 8:1 Cryogenic Multiplexer for Josephson Arbitrary Waveform Synthesizer

Yerzhan Kudabay<sup>1</sup>, Paul Julius Ritter<sup>2</sup>, Vadim Issakov<sup>1</sup> Institute for CMOS Design, TU Braunschweig,

- Braunschweig, Germany Institute for Electrical Measurement Science and

- Fundamental Electrical Engineering, Technical University Braunschweig, Braunschweig, Germany

# 4:40-5:00 PM - A Direct Digital Synthesizer-based

# **Arbitrary Waveform Generator for Envelope Modulation** in Trapped-Ion Quantum Computer Operating at 4K Paul Shine Eugine<sup>1</sup>, Peter Toth<sup>1</sup>, Kaoru Yamashita<sup>2</sup>, Sebastian Halama3, Christian Ospelkaus3, Hiroki Ishikuro2,

- Vadim Issakov<sup>1</sup> Institute for CMOS Design, TU Braunschweig, Braunschweig, Germany

- <sup>2</sup> Ishikuro Laboratory, Keio University, Yokohama, Japan

- <sup>3</sup> Institute of Quantum Optics, Leibniz University, Hannover, Germany

# 7b.4 5:00-5:20 PM - A Low-Power, High-Swing LDMOS Driver

Amplifier for Shuttling Controller in a Trapped-Ion Quantum Computer Operating at 4K

Zhaoqun Guo¹, Alexander Meyer¹, Adilet Dossanov¹, Paul Julius Ritter², Marius Neumann², Jens Repp³, Matthias Brandl<sup>3</sup>, Meinhard Schilling<sup>2</sup>, Vadim Issakov<sup>1</sup> Institute for CMOS Design, TU Braunschweig,

Braunschweig, Germany

<sup>2</sup> Institute for Electrical Measurement Science and Fundamental Electrical Engineering, TU Braunschweig, Braunschweig, Germany

<sup>3</sup> Infineon Technologies AG, Neubiberg, Germany

| W | EDN | IESD. | ΑY |  |

|---|-----|-------|----|--|

|   |     |       |    |  |

|   |     |       |    |  |

8a. Reliability and physics of Si/SiGe bipolars

Wednesday 8:30AM Ballroom Session Chair: Kai Kwok, Skyworks

Co-Chair: Jonggook Kim, Texas Instruments

8:30-8:50 AM - High Temperature Annealing induced recovery of Hot-Carrier degradation in High Performance NPN SiGe HBTs

Dimitris P. Ioannou and Adam DiVergilio GlobalFoundries, USA

8a.2 (Student)

8:50-9:10 AM - Using Pulsed-Mode Measurements of SiGe HBTs for Non-Destructive, Improved RF-SOA **Estimation**

Nelson E. Sepúlveda-Ramos, Harrison P. Lee, Jeffrey W. Teng, and John D. Cressler School of Electrical and Computer Engineering.

Institute of Technology, Atlanta, GA 30332-0250 USA

8a.3 (Student)

9:10-9:30 AM - The Effect of Base Doping Profile on Horizontal Current Bipolar Transistor's (HCBT) Beta

Recovery at Cryogenic Temperatures Filip Bogdanović<sup>1</sup>, Lovro Marković<sup>1</sup>, Azra Tabaković<sup>1</sup>, Josip Žilak<sup>2</sup>, Marko Koričić<sup>1</sup> and Tomislav Suligoj<sup>1</sup> <sup>1</sup>University of Zagreb, Faculty of Electrical Engineering and

Computing, Micro and Nano Electronics Laboratory, Zagreb, Croatia <sup>2</sup>Ericsson Nikola Tesla d.d., Zagreb, Croatia

9:30-9:50 AM - On the Emitter Back-Injection Current in Advanced SiGe HBTs at Cryogenic Temperatures

Xiaodi Jin, Prateek Kumar, and Michael Schröter Chair for Electron Devices and Integrated Circuits, Technische Universität Dresden, Germany

8a.5 (Student)

9:50-10:10 AM - TCAD-Based Design of SiGe HBT Germanium Profiles via Bayesian Optimization Justin P. Heimerl, Jeffrey W. Teng, Harrison P. Lee, Delgermaa Nergui, Jackson P. Moody, and John D. Cressler School of Electrical and Computer Engineering, Georgia

8b. mmW Metrology & Power Amplifier Technology Wednesday 8:30AM Studio 2.3.4

Institute of Technology, Atlanta, GA 30332-0250 USA

Session Chair: Harris Moyer, HRL Laboratories, LLC. Co-Chair: Utku Soylu, IBM T.J. Watson Research Center

8b.1 (Invited)

8:30-9:10 AM - Trends in Millimeter-Wave and THz Test Equipment Eric Bryerton, Jeffrey Hesler

Virginia Diodes, Inc., Charlottesville, VA, USA

9:10-9:30 AM - A D-band Power-Combined Stacked Common-Base Power Amplifier Achieving 20.9 dBm Psat and 24.3 % PAE in a 250-nm InP HBT Technology

Arno Hemelhof\*†, Sehoon Park‡, Yang Zhang\*, Mark Ingels\*, Giuseppe Gramegna\*, Kristof Vaesen\*, Dongyang Yan\*†,

Piet Wambacq\*†

\*imec, Leuven, Belgium

<sup>†</sup>Vrije Universiteit Brussel, Dept. of Electronics and Informatics (ETRO), Brussels, Belgium \*now with Kyungpook National University, School of

Electronics Engineering, Daegu, Republic of Korea

8b.3

9:30-9:50 AM – A Two-stage, Two-way-combined, 220-GHz Power Amplifier With 17.1% PAE in a 250-nm InP **HBT Process**

Eythan Lam#, Jeff Shieh-Chieh Chien#\$, Petra Rowell\*,

Miguel Urteaga\*, James Buckwalter# #University of California, Santa Barbara, USA

\$Samsung Semiconductor, Inc., San Jose, USA

\*Teledyne Scientific and Imaging, Thousand Oaks, USA

8b.4 9:50-10:10 AM - 10-GSymbols/s Supply Modulated 250-GHz SiGe HBT Transmitter RF Front-End with 6.8-dBm **Peak Modulated Power** Haidong Guo¹, Suprovo Ghosh¹, Frank Zhang¹, Suhwan Lee¹, Wooyeol Choi², Shenggang Dong¹, Kenneth O¹

<sup>1</sup>University of Texas at Dallas, Richardson, TX, USA <sup>2</sup>Seoul National University, Seoul, Korea

9a. Diamond and Novel III-V Designs for High Power Wednesday 10:30 AM Ballroom

Session Chair: Kanin Chu, BAE Systems Co-Chair: Takuya Hoshi, NTT

9a.1 (Invited) 10:30-11:10 AM - Diamond-BN Heterojunctions for High Power Devices: The Ultimate HEMT? T. Thornton

Arizona State University, Tempe, AZ USA

9a.2

11:10-11:30 AM - Exploring Breakdown Voltage Improvement in 20-nm InGaAs-Channel HEMT-OI with **Metallic Back-Gate** A. A. Kunnath, M. Moulin, S. A. Albahrani, D.

Schwantuschke, and A. Leuther Fraunhofer IAF, Freiberg, Germany

# 9b. Receiver Circuits

Robin Ying and Joe Tai

9b.3 (Student)

Wednesday 10:30 AM Studio 2.3.4 Session Chair: Gregory Flewelling, BAE Systems Co-Chair: Django Trombley, TI

10:30-10:50 AM - A 19.1-dBm-Linear 2-20 GHz N-path Down-converter in HRL 40-nm GaN for Resilient Receivers

HRL Laboratories LLC, Malibu, CA, USA

9b.2 10:50-11:10 AM - Single-Chip 30 GHz SiGe Sub-Sampling

PLL with 28.3 fs Jitter

Dimitre Dimitrov, Mark D. Hickle, Matthew Speir, Joseph M. Krzyzek, Daniel P. Lacroix, Shail Srinivas, Robert Sepanek,

Spencer Desrochers, and Steven Eugene Turner BAE Systems, Merrimack, NH, USA

11:10-11:30 AM - Design of an Ultra-Low Phase Noise Broadband Amplifier in 130 nm SiGe BiCMOS Technology

Vijayalakshmi Surendranath Shroff, Meysam Bahmanian, Stephan Kruse, and J. Christoph Scheytt

Paderborn University, Department of Electrical Engineering, Heinz Nixdorf Institute, Germany

# 10. Late News Wednesday 1:00 PM Ballroom

Session Chair: Jack Pekarik, GlobalFoundries Co-Chair: Sadayuki Yoshitomi, MegaChips Corporation

10.1

1:00-1:20 PM - Design of a Terahertz InP HBT Quadrupler and Silicon Interposer

Vinay Iyer<sup>1,2</sup>, Christopher Moore<sup>2</sup>, Prerana Singaraju<sup>2</sup>, Matthew F. Bauwens<sup>3</sup>, Steven M. Bowers<sup>2</sup>, Robert M.

Weikle<sup>2</sup> <sup>1</sup>Nokia of America Corporation, Sunnyvale, CA, USA <sup>2</sup>University of Virginia, Electrical and Computer Engineering,

Charlottesville, VA, USA <sup>3</sup>Dominion Microprobes, Charlottesville, VA, USA

# 10.2

1:20-1:40 PM - A 130-GHz Bandwidth 61-dBOhm Variable-Gain Differential Linear TIA in a 130-nm SiGe:C **BiCMOS Technology**

Thiemo Herbel<sup>1</sup>, Mohsin Tarar<sup>2</sup>, Frank Vater<sup>3</sup>, Dietmar Kissinger<sup>1</sup>

<sup>1</sup>Institute of Electronic Devices and Circuits, Ulm University, Ulm, Germany

<sup>2</sup>Department of Electronics Engineering, University of Chakwal, Chakwal, Pakistan

<sup>3</sup>Leibniz Institute for High Performance Microelectronics (IHP), Frankfurt (Oder), Germany 10.3

1:40-2:00 - 140-GHz Transmit and Receive Front-end

Circuits with 10.8-dBm Psat and 5.9-dB NF in a 45-nm **BiCMOS SOI Process** Wonho Lee, Everett O'Malley, James Buckwalter Electrical & Computer Engineering, UC Santa Barbara, Santa

Barbara, CA 10.4

2:00-2:20 - The Design of Wideband LNAs in 45nm SiGe **BICMOS**

David Dolt1, Mingi Yeo1, David Reents1, Will Gouty2, Tony Quach<sup>2</sup>, Samuel Palermo<sup>1</sup>

<sup>1</sup>Texas A&M University, Analog and Mixed-Signal Center,

College Station, TX, USA <sup>2</sup>Air Force Research Laboratory, Sensors Directorate,

WPAFB, OH, USA

10.5 2:20-2:40 - Ka-Band MMIC Implementation of a Load-**Modulating Loop Combiner Power Amplifier**

Osian Jones, Taylor Barton RF Power and Analog Laboratory, University of Colorado Boulder, Boulder, CO, 80309 USA

# **EXECUTIVE COMMITTEE**

Tomislav Suligoj University of Zagreb, Symposium

Chair

Breandán Ó hAnnaidh Analog Devices, Symposium Co-

Michael Roberg , Qorvo, Technical Program

Chair

TU Dresden. Primer Course Michael Schroter

Chair

Doug Weiser Texas Instruments, Short Course

Chair

Jack Pekarik GlobalFoundries, Publications

Chair

Sadayuki Yoshitomo MegaChips Corp., Publications Co-

Chair

Chair

Raytheon Technologies, Treasurer Jon Mooney

Patrick Fay

Chair NTT Corporation, Publicity

University of Notre Dame, Exhibition

Ciena Corporation, JSSC Guest

∩MF

BÆ

BAE Systems,

Munehiko Nagatani

Chair

Yuriy Greshishchev

Editor

Lei Zhang

NXP Semiconductors, Local Arrangements Chair

Rob Howell Northrup Grumman, Emeritus

Member Craig Steinbeiser Qorvo, Emeritus

Member NXP Semiconductors, Emeritus Bruce Green

Member

# TECHNICAL PROGRAM COMMITTEE

Analog ICs

Sri Navaneeth Easwaran Texas Instruments,

Chair Annamalai Muthukumaraswamy

Labs University of California, San

Hanh-Phuc Le

Diego University of Texas at

Brian Ma

Dallas

RF and Microwave ICs Mike Litchfield

Chair

Michael Roberg

Qorvo

Jim Carroll

AmpliTech

Shuoqi Chen

Qorvo

Nabil El-Hinnawy

TowerJazz

Greg Flewelling

Systems Toshihide Kuwabara NFC:

Corporation

Raytheon Jon Mooney

Technologies

Frank van Vliet

TNO

Simon Wood

MACOM

Kazuya Yamamoto Mitsubishi Electric

Corporation

Jason May

MACOM

Texas

Django Trombley

Instruments

Northrop Farooq Amin

**David Wohlert**

Grumman

Qorvo

Mike Coffey

Boeing

Simon Mahon Macquarie University Kevin Kobayashi Qorvo **Compound Advanced Devices and Technologies** University of Notre Dame, Patrick Fay Chair Tim Vasen Northrup Grumman Mission Systems Ken Chu BÆ Systems NΑΡ Bruce Green Semiconductors Rob Howell Northrup Grumman Mission Systems Takuya Hoshi NTT Device Technology Laboratories Sumitomo Electric Industries, Ken Kikuchi Ltd. Elaheh Ahmadi University of California, Los Angeles University of Illinois at Lucy Shi Chicago Akio Wakejima Nagoya Institute of Technology

# **Compound Semiconductor Modeling**

NXP Semiconductors, Lei Zhang Chair

Subrata Halder Qorvo

Masaya Iwamoto Keysight Technologies

Yueying Liu MACOM

Cardiff

Paul Tasker

University University of

Lan Wei Waterloo

Rached Hajji

John Robert (Rob) Jones BÆ

Systems

Kaiman Chan Texas Instruments

**Device Physics** Vibhor Jain GlobalFoundries, Chair University of Tomislav Suligoj Zagreb Martin Claus Infineon Guanghai Ding Analog **Devices** Jonggook Kim Texas Instruments Kai Kwok Skyworks High Speed Digital, Mixed-Signal, and Optoelectronic ICs Mahdi Parvizi Cisco Systems, Chair Munehiko Nagatani NIT Corporation Yuriy Greshishchev Ciena Corporation Koichi Murata Renesas The' Linh Nguyen Marvell Johann-Christoph Scheytt Paderborn University Craig Steinbeiser Qorvo Sorin Voinigescu University of Toronto mm-Wave and THz ICs Frank van Vliet TNO.Co-Chair Harris Moyer HRL Laboratories, Co-Chair Nils Pohl Ruhr-University **Bochum** Penn State Wooram Lee University Remy Leblanc MACOM Leonardo Vera Analog Devices Akshay Visweswaran Nokia Bell Labs Kazuya Yamamoto Mitsubishi Electric Corporation Marcus Pan SRC IBM T.J. Watson Research Utku Soylu Center Ignacio Ramos HR. Laboratories Shenggang (Daniel) Dong Samsung Research America Maxwell Duffy Northrop Grumman Silicon and Related Alloy Semiconductor Modeling Saurabh Sirohi GlobalFoundries, Chair Sadayuki Yoshitomi MegaChips Corp. Breandán Ó hAnnaidh Analog Devices Andreas Pawlak Infineon Nicolas Derrier STMicroelectronics Paulius Sakalas MPI Corporation/ ATV Michael Schroter W Dresden Sebastien Fregonese MS Bordeaux Pete Zampardi Qorvo

Silicon and Related Alloy Semiconductor Processing Qorvo, Pete Zampardi

Chair

Josef Boeck

Infineon

NΑΡ Johan Donkers

Semiconductors Alexis Gauthier

STMicroelectronics Jack Pekarik

GlobalFoundries

Holger Rucker HP Microelectronics

Stan Phillips

Tower

Michael Peters **Applied**

Materials

Hiroshi Yasuda Texas

Instruments

# SYMPOSIUM EVENT MANAGEMENT

Catherine Shaw C.Shaw,

LLC

John Hinch Omnipress

IEEE Electron Devices Jessica Lotito

Society

Jim Skowrenski **IEEE Electron Devices**

Society

Sherry Russ Sills IEEE Meetings, Conferences and **Events**

Kristen Macarthur

IEEE Meetings, Conferences and

**Events**

# LOOKING TOWARDS THE FUTURE

The 2025 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS) will be held on October 12-15, 2025

INTEGRATED CIRCUITS and DEVICES in GaAs, InP, GaN, SiGe, and other compound semiconductor and CMOS technologies

Scottsdale, Arizona, USA

Sponsored by the IEEE Electron Devices Society, co-sponsored by the Solid-State Circuits Society and the Microwave Theory & Techniques Society

# **CALL FOR PAPERS**

The 2025 BCICTS will be held in Scottsdale, Arizona, USA from October 12-15, 2025. Subject area groupings for paper submissions are as follows:

HIGH-SPEED DIGITAL, MIXED-SIGNAL, AND OPTOELECTRONIC ICS Mixed analog/digital ICs - Digital ICs - (high-speed) DACs and ADCs - Networking ICs, MUX/DEMUX, Clock and data recovery, Decision circuits, Equalizers - Optical data links, Laser and modulator drivers, optoelectronics and photonics ICs

## ANALOG, RF, AND MICROWAVE ICs

Op amps - Voltage references and regulators - Integrated filters - Sensors and actuators - RF circuits and systems - Radio and transceiver subsystems - LNAs - AGCs - Mixers - Voltage controlled oscillators - Frequency synthesizers - Power amplifiers - RF switches - Noise and distortion suppression - RF Packaging - Integrated RF passives. Analog, RF, power conversion, High-voltage ICs - Biomedical electronics - Power Management ICs - Energy harvesting ICs - Motor controls - Analog subsystems within a VLSI chip - Packaging of high-performance ICs.

# mm-WAVE AND THZ ICs

Millimeter - wave circuits and systems - THz circuits and systems. MM-Wave switches and amplifiers. Phased-array antenna circuits

# DEVICE PHYSICS:

New device physics phenomena in Si, SiGe, SiC, GaN, MOS, and III-V HBTs and FETs - Device design issues and scaling limits - Hot electron effects and reliability physics - Transport and high field phenomena - Noise - Linearity/Distortion - Novel measurement techniques - Operation in extreme environments (low/high temperatures, radiation effects), and ESD phenomena.

### MODELING AND SIMULATION

Improved silicon-based BJT and HBT models and physics-based modelling techniques - Improved III-V HBT and FET models and physics-based modelling techniques - Parameter extraction methods and test structures - High-frequency measurement, calibration and de-embedding techniques - RF and thermal simulation techniques - Modelling of passives, interconnect and packages - Statistical modelling - Device, process and circuit simulation - CAD/modelling of power devices - Packaging of power devices.

### PROCESS AND DEVICE TECHNOLOGY

Device and IC manufacturing processes, testing methodologies, & reliability - Integration of III-V devices on Si - High performance devices such as GaN power conversion devices - near-THz SiGe HBTs & InP HEMTs - Novel devices such as tunnel FETs (TFETs) - carbon nanotubes, MEMS, graphene & diamond transistors. Optoelectronic and photonic devices such as optical modulators, lasers, photodetectors, and Silicon Photonics - Thermal management technologies, thermal simulation - Advanced packaging of high-power devices and ICs. Advances in processes and device structures demonstrating high speed, low power, low noise, high current, high voltage, etc. BiCMOS processes - Advanced process techniques - Si and SiC homojunction bipolar/BiCMOS devices and

SiGe heterojunction bipolar/BiCMOS devices - Manufacturing solutions related to Bipolar and BiCMOS yield improvements -Fabrication of high-performance passive components, sensors, and MEMs - Process technology related to discrete and integrated bipolar/BiCMOS power devices - IGBT, RF power devices. Wide

bandgap bipolar devices (e.g., SiC) and related process technology -

3D Integration - Reliability and testing for IC manufacturing

**IMPORTANT DATES** Friday May 9, 2025 - Abstracts Due

Friday, July 11, 2025 - Decision E-mail Sent Friday, September 5, 2025 - Final Manuscript Due

Authors must submit an abstract (not more than 4 pages including figures and other supporting material) of results not previously published or not already accepted by another conference. Papers

will be selected on the basis of the abstract. The abstract must concisely and clearly state:

a)The purpose of the work

b)What specific new results have been obtained c)How it advances the state-of-the-art or the industry

d)References to prior state-of-the-art

- e)Sub-committee preference: • Analog, RF, and Microwave ICs

- Device Physics

- High-Speed Digital, Mixed-Signal, & Optoelectronic

- Modeling & Simulation

- · mm-Wave and THz ICs

- Process & Device Technology

categories. Company and governmental clearances must be obtained prior to

Abstracts must include: title, author(s) name(s) and affiliation(s), corresponding authors' postal and e-mail addresses, and telephone numbers. The committee will honor the authors' committee preference but reserves the right to review the paper in other

submission of the abstract.

Accepted work may be used for publicity purposes. Portions of the abstracts may be quoted in articles publicizing the Symposium. Please note on the abstract if this is not acceptable.

Abstracts (PDF only) must be submitted electronically.

Authors will be informed of a decision by July 11, 2025. Authors of accepted papers are required to submit a 4-page camera-ready PDF

by September 5, 2025 for inclusion in the Symposium Digest. Further questions on abstract submission may be addressed to the

Symposium Technical Chair:

Technical Director, MMIC Design Qorvo, Inc.

Michael Roberg

Email: michael.roberg@qorvo.com

Symposium information, including abstract submission instructions and a link to the abstract submission system will be available on the BCICTS website at: http://www.bcicts.org in the near future.

# 2024 BCICTS SPONSORS

-PLATINUM-

-GOLD-

SILVER-

-BRONZE-

# **RichWave**

-EXHIBITORS -

# **Future RF Technologies & Solutions**

# **Application**

Networking

Mobile

**Smart Home**

loT

Wireless Media

Broadcasting

**Automotive**

# Everyone and Everything Together

- Completed RF Portfolio and Radar Sensor

- Advanced Technologies Capabilities with high performance

- High Reliability and Quality Assurance

SW

Filter

Sensor

# Connect with RichWave

# QOCVO.

# Brilliant Mind?

Solve the most complex RF and power design challenges at Qorvo.

Join Qorvo's world-class engineers and make a future in RF and power technology.

qorvo.com/careers

We have a long history of globally owned, regionally diverse internal manufacturing operations, including wafer fabs, assembly and test factories, and bump and probe facilities across 15 worldwide sites. We manufacture tens of billions of analog and embedded processing semiconductors annually, across more than 80,000 different products, and deliver them to more than 100,000 customers around the globe.

TEXAS INSTRUMENTS

FOR JOINING US IN BEAUTIFUL FT. LAUDERDALE!

WE LOOK FORWARD TO SEEING YOU FOR BCICTS 2025 IN SCOTTSDALE, AZ, USA!

www.bcicts.org